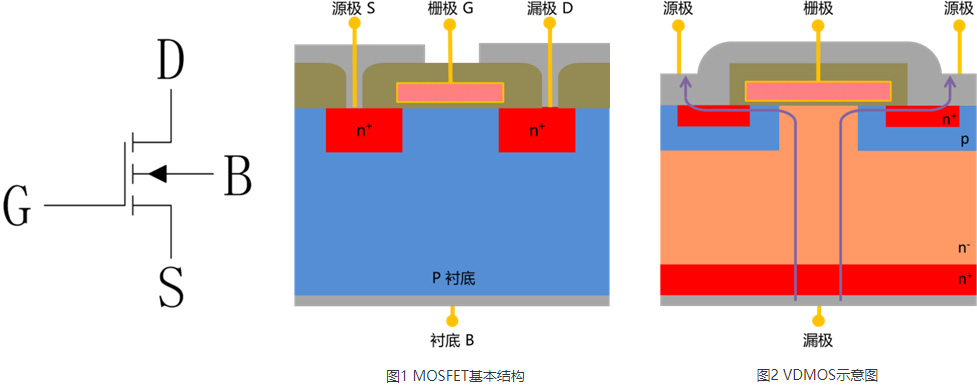

金属-氧化层-半导体场效应晶体管(MOSFET)是集成电路设计中的基本单元,它的电路符号和器件结构如图1所示。典型n沟道MOS器件具有4个电极,并连接不同的电压偏置。一般情况下源极和衬底极接低电位,比如接地。不工作时器件处于截止状态,此时器件的源极和漏极之间没有导电通道,相当于开关的断开状态。当栅极加上一个大于Vgs(th) 的正电压后,栅极氧化层下方的p型衬底表面会产生反型层, 即导通沟道。沟道连通了器件源极和漏极,此时NMOS相应的处于了导通状态。栅极电压越高,导通越充分。

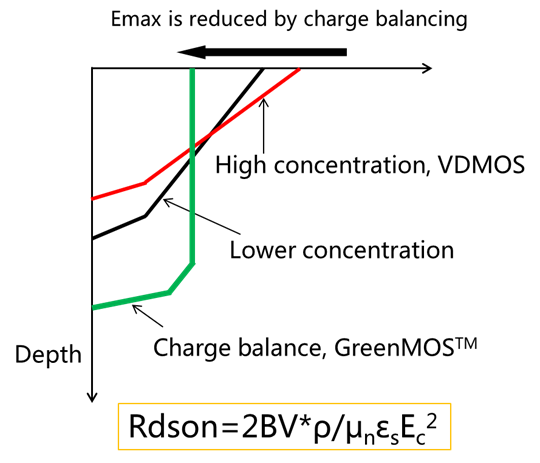

中高压功率MOSFET通常采用垂直沟道结构,如图2所示,器件的漏极在芯片底部,源极在芯片顶部,整个器件呈垂直结构放置。这种结构被称为Vertical Double-diffusion MOS (VDMOS)。从结构上看VDMOS的漏极从原来的表面位置移到了器件的底部,漏极电流也相应从器件的底部流到器件的表面,变成了垂直型器件。漏极电流与沟道之间的区域是漂移区,是高压功率器件用来耐压的主要部分。漂移区越厚且漂移区电阻率越低,则耐压越高,而与此同时器件的导通电阻相应的也就越高。这是因为VDMOS的Rdson 与BVdss的2~2.5次方成正比。即公式1:

Rdson = a* BV2~2.5

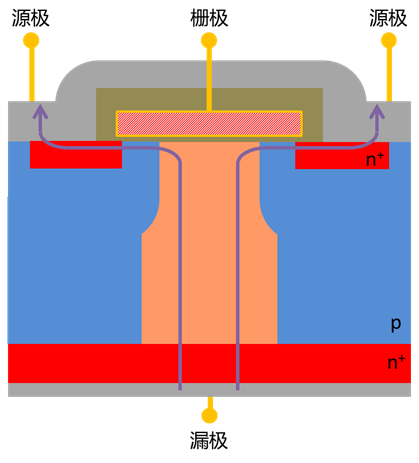

超级结MOSFET可以打破这个限制,其基本结构如图3所示。它和VDMOS相比最大的区别就是在p-body下方加入了p柱,使漂移区中出现了交替的pn结结构。利用相邻的pn柱之间相互耗尽的原理,将漂移区的浓度可以提升,使得器件导通时电阻率降低。而在关态时,p柱和n柱之间可以相互耗尽,使耗尽区尽量扩大,维持了较高的耐压,由此打破了公式1的硅极限,使导通电阻与击穿电压达到近似线性的关系,显著提高了器件性能。

图3 SJ VDMOS示意图

相对于普通VDMOS器件,超级结功率器件的速度更快,FOM更低,但是也会带来其他的一些负面问题,比如高di/dt & dv/dt造成的栅极振荡及EMI问题。因此,超级结的设计十分讲究,设计不当则容易导致芯片的震荡而使器件出现EMI超标的问题。